Soc Architecture Tutorial

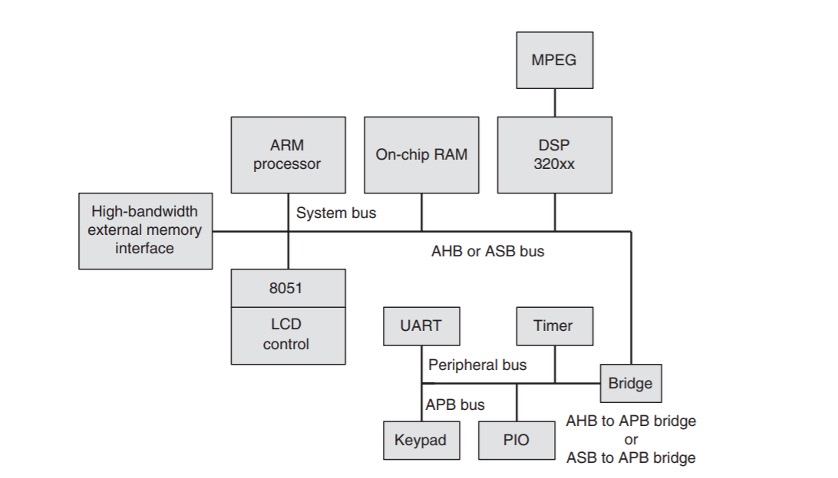

The ARM Advanced Microcontroller Bus Architecture AMBA is an open-standard on-chip interconnect specification for the connection and management of functional blocks in SOC designs. Key aspects of this paper are highlighted in an on-line video series A Look Inside.

Low Power Design for SoCs ASIC Tutorial SoC Clock9 MJ.

Soc architecture tutorial. Transistor gate lengths are now in term of nano meters. Second the Zynq design flow is described and shown in a flowchart. Ad Learn SoC Online At Your Own Pace.

Low Power Design for SoCs ASIC Tutorial SoC Clock10 MJ. This module provides a high-level view of the device architecture including the C66x DSP and ARM Cortex-A15 processors memory and transport topologies networking and interface enhancements as well as power saving and debug features for KeyStone II DSPARM. Ad Learn SoC Online At Your Own Pace.

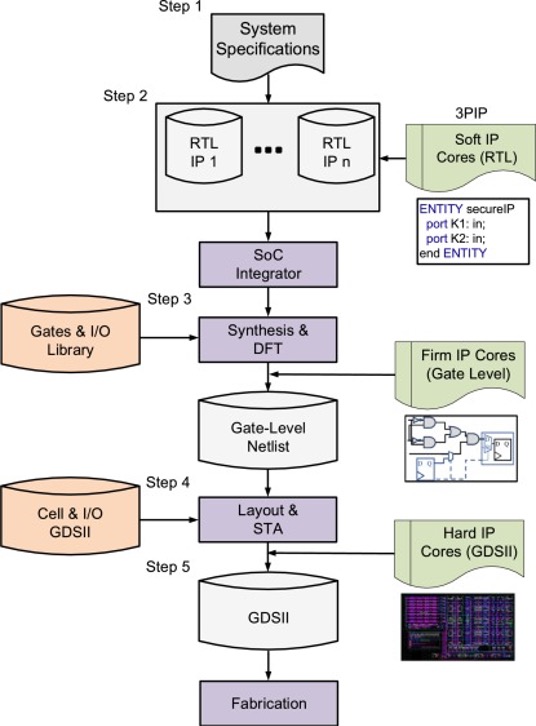

An SoC design is a product creation process which Starts at identifying the end-user needs Ends at delivering a product with enough. Beside classical concerns regarding database availability integrity and. Scalability of communication architecture Disadvantages.

In this tutorial we will first learn about the most common of those which is the AMBA family of bus protocols. The only SOC specific operation to be performed by this Box type is a basic level of correlation in order to identify and fuse duplicates either from the same or different sources. This tutorial is designed for software programmers who would like to understand the concepts of SOA.

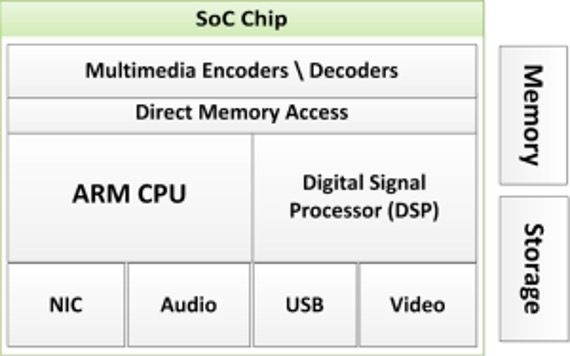

Start Today and Become an Expert in Days. In this article the Zynq-7000 all programmable SoC architecture is explained. System-On-Chip System A collection of all kinds of components andor subsystems that are appropriately interconnected to perform the specified functions for end users.

NOC and SOC Design 22 SOC Communication Structures Network on Chip Advantages Structured architecture Lower complexity and cost of SOC design Reuse of components architectures design methods and tools Efficient and high performance interconnect. Third the processing system PS and programmable logic PL which are located inside the Zynq are described in more detail. Introduction SoC Architecture SoC Design SoC Applications Summary Refferences Outline 3.

The ALU result from the EXMEM register is always fed back to the ALU input latches. Irwin PSU 1999 Gated Clock FSM Architecture Clock Gated Clock Comb Reg Logic AF Latch AF - Activation Function Which evaluates to logic 1 when clock needs to be stopped. KeyStone II DSPARM SoC Architecture Overview.

First the general information about the structure of the Zynq is provided. 12 Lectures to CST II A current-day system on a chip SoC consists of several di erent microprocessor subsystems together with memories and IO interfaces. Irwin PSU 1999 Clock Tree Construction to Facilitate.

If the forwarding hardware detects that the previous ALU operation has written the register corresponding to the source for the current ALU operation control logic. D Boxes are the more standard modules we find in a SOC architecture. November 1 2012.

This Architecture Brief is designed to help system architects engineers and managers decide if SoC FPGAs are a potential fit for their application. SOC Consortium Course Material 22 Forwarding Architecture Forwarding works as follows. 14 Architectural Design Exploration 16 High-level Design Capture and Synthesis 01 SoC Design.

Approximately every 18 months the number of transistors on a chip doubles Moores law. Introduction Technological Advances todays chip can contains billions of transistors. This course covers SoC design and modelling techniques with emphasis on.

The complication of each service is not noticeable to other service. The Service Oriented Architecture is an architectural design which includes collection of services in a network which communicate with each other. SoC FPGAs which can be.

Start Today and Become an Expert in Days. SoC LevelTop Level view Feature Extractions During SoC design verification you must view the design at the top level and extract its SoC level functionalityfeatures during specification study phase for its verificationAt this stage a thorough understanding of SoC functionality and its architecture is required because misunderstanding of the specification can become the leading cause. Interfaces block verification clock architecture and test strategy Fixed point architecture exploration and design How - Quickly assemble architectures for exploration to.

Join Millions of Learners From Around The World Already Learning On Udemy. Join Millions of Learners From Around The World Already Learning On Udemy.

System On Chip Vlsi Tutorial Mepits

Https Www Ee Ryerson Ca Courses Coe838 Lectures Intro Soc Pdf